The Current Status of SoC Chips in Automotive Industry

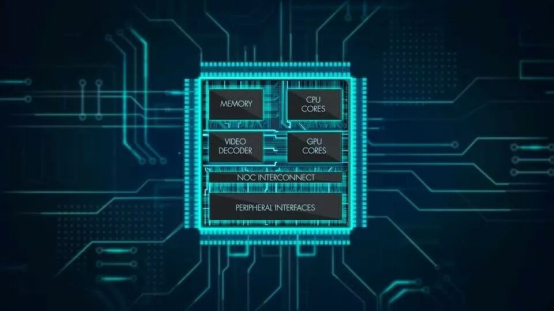

SoC stands for System-on-a-Chip, which means “putting the whole system on a chip” in Chinese. This concept first originated from the development of smartphones, where manufacturers integrated CPU, GPU, memory, Modem, ISP, DSP, codec, and other system components into a single chip, eliminating the need to separately purchase these functional chips. This brought benefits such as saving motherboard space, cost, and power consumption, making it attractive for smartphones that prioritize slim and long-lasting design.

The first application of SoC in cars was in the intelligent cockpit field. With the development of intelligent cockpits, powerful CPU computing power is required to improve task processing capabilities, robust GPU computing power is needed to process unstructured data such as videos and images, efficient AI computing power to meet intelligent cockpit’s interactive experience requirements, high-speed DSP computing power to achieve large bandwidth real-time communication, and mobile operating system compatibility to rapidly enhance entertainment experiences. In short, intelligent cockpits’ needs in 4G communication, in-car WIFI, driver gesture recognition, high-quality audio and video processing, coding, image stitching and other typical application scenarios align closely with smart devices. Thus, Qualcomm, with its technological strength and brand advantages in consumer electronics and communication areas, based on the Snapdragon 600 platform, created the Snapdragon 620A automotive graded SoC chip in 2014, which has been tremendously successful. As of now, Qualcomm’s intelligent cockpit SoC chip has evolved to the fourth generation SA8295.

In the field of autonomous driving, massive frame image processing severely tests the chip’s parallel computing capabilities. CPUs, which excel in logic and digital computing, are incapable of handling a large number of parallel simple computing tasks. Therefore, SoC chips that integrate CPUs and XPUs (GPUs/NPUs/TPUs) are commonly used in autonomous driving. As self-driving technology advances, the computing power of SoC in autonomous driving is continuously improving. Currently, the mass-produced SoC with the highest AI computing power is NVIDIA Orin.

Due to the different scenarios between smart cabins and smart driving, and the different emphasis on computing power, smart cabin SoC and smart driving SoC have been parallelly developed for a long time. In September this year, Qualcomm and NVIDIA almost simultaneously released their own automotive supercomputing chips, Thor (NVIDIA) and Snapdragon Ride Flex (Qualcomm), both of which can support both smart cabin and smart driving functions. The industry couldn’t help but wonder if the era of cabin-driving integrated chips is coming. In this regard, the author believes that there is still a long way to go to truly achieve cabin-driving integration.

Due to the different scenarios between smart cabins and smart driving, and the different emphasis on computing power, smart cabin SoC and smart driving SoC have been parallelly developed for a long time. In September this year, Qualcomm and NVIDIA almost simultaneously released their own automotive supercomputing chips, Thor (NVIDIA) and Snapdragon Ride Flex (Qualcomm), both of which can support both smart cabin and smart driving functions. The industry couldn’t help but wonder if the era of cabin-driving integrated chips is coming. In this regard, the author believes that there is still a long way to go to truly achieve cabin-driving integration.

First, smart cabin and smart driving have different functional safety levels, and how to create an OS that can simultaneously take care of different functional safety levels is a challenge.

Second, true cabin-driving integration requires flexible allocation of computing power. However, Thor currently uses static configuration, which means that once the computing power is allocated, it cannot be switched according to the scenario.

Third, many car companies have different departments for smart cabins and smart driving, and how to allocate work and collaborate within a single chip is also a challenge, with no mature experience to follow.

Therefore, for a period of time in the future, it is still mainstream to have smart cabin SoC and smart driving SoC in different chips.

In fact, whether it is cabin-driving integration or independent development of smart cabins and smart driving, in order to understand the future development direction of automotive SoCs, one must first answer a question: What determines the direction of development of automotive SoC chips?

Challenges of Automotive Intelligence

Cao sir believes that the development direction of automotive SoC chips is determined by the development of the overall vehicle electronic and electrical architecture!

The electronic and electrical architecture was first proposed by Delphi Corporation. It is a concept that combines the principle design of the car’s electronic and electrical system, the design of the central electrical box, the design of connectors, the design of the electronic and electrical distribution system, and other designs into a single solution. According to the widely accepted definition of Bosch in the industry, the electronic and electrical architecture is divided into three stages: distributed architecture, domain centralized architecture, and central centralized architecture. In recent years, with the rapid development of the “New Four Modernizations” of automobiles, many car companies have moved from distributed electrical architectures to domain-centralized electrical architectures, and some have even taken a step toward central centralized electrical architectures. The overall trend of the rapid evolution of electronic and electrical architecture is driven by the four major challenges facing automobiles: “weight reduction and cost reduction,” “intelligent networking,” “rapid iteration,” and “business model disruption.”## Challenge of “Weight Reduction and Cost Reduction”

With the increasing number of intelligent functions on cars, traditional distributed architectures can lead to a high number of controllers, and thus, a high cost and weight issues. According to statistics, a traditional high-end vehicle based on distributed electronic architecture may require more than 70 controllers, with a total weight of 80Kg for the entire electrical system.

Challenge of “Intelligent Connected Cars”

Under the new wave of industrial transformation, an intelligent connected car collects at least 10TB of data per day, and thus demands higher requirements for communication between the vehicle and the external world. Traditional electronic architectures based primarily on CAN communication will not be able to support these needs.

Challenge of “Rapid Iterations”

Traditional low-cohesion, high-coupling electrical architectures may have poor reusability, scalability, and a long development cycle, leading to high costs. With the fast-paced market, traditional distributed electronic architectures are not suitable, as adding an intelligent function requires cooperation from many controllers, resulting in high costs and a long development cycle.

Challenge of “Business Model Disruption”

The traditional profit model of “selling vehicles and after-sales service” is now changing to a subscription-based profit model on the internet. Traditional signal-oriented electrical architectures cannot support this subscription model, so the service-oriented SOA electrical architecture has emerged.

Development Direction of Vehicle SoC chips

To meet the above four challenges, a new type of electrical architecture needs to have eight core features, which are “low power consumption,” “trustworthiness and reliability,” “high integration,” “reusability,” “scalability,” “high performance,” “low coupling,” and “high openness.” Among these, “high performance,” “low power consumption,” “high integration,” and “trustworthiness and reliability” will determine the development direction of vehicle SoC chips.

“High Performance”

Since scenarios such as multi-screen interconnection, intelligent interaction, and intelligent driving require high chip performance, the CPU computing power of intelligent cabins has shown a significant increase in recent years. In less than seven years, the performance has improved from a few KDMIPS to over 100 KDMIPS. With the development of autonomous driving, the AI computing power of ADAS chips has also significantly increased. Typically, the industry believes that to achieve level 2 automated driving assistance, the computing power required is less than 10 TOPS. Level 3 requires 30-60 TOPS, level 4 requires more than 300 TOPS, level 5 requires over 1000 TOPS or even over 4000+ TOPS.### “Low Power Consumption”

According to preliminary estimates, every 50W increase in power consumption would cause a loss of 8-10km in driving range of a new energy vehicle under the CLTC working condition. Therefore, the new electronic and electrical architecture has put forward higher requirements for chip energy efficiency ratio besides enhancing the process nano-level. In addition to improving the process nano-level, the transition from general chips to ASIC chips with “tailor-made” algorithms for certain types is a promising path for reducing power consumption. The current solution for autonomous driving chips is the use of GPU+FPGA. After the algorithm becomes stable in the future, ASIC will become mainstream. At present, the energy efficiency ratio of mainstream products has evolved from the initial 0.8TOPS/W (EyeQ4) and 1TOPS/W (Xavier) to 4.44TOPS/W (NVIDIA Orin) and 4.8TOPS/W (Horizon Journey 5), and the power consumption of future mainstream products will be at least 6TOPS/W or higher.

“High Integration”

The automotive electronic and electrical architecture (E/E Architecture) is gradually evolving from the traditional distributed system to the centralized system. In the centralized E/E architecture, new domain controllers integrate more functions. If the main control chip is to match its function, the computing power and performance must be improved accordingly. Under this trend, automotive chips are gradually shifting from the general, distributed MCU (single function chip) to the customized and integrated SoC (system on chip) with multiple functions. SoC is a system-level chip that integrates key components of the system on one chip. It can improve performance while effectively reducing the development cost of the system product, shortening the development cycle, and enhancing the product’s competitiveness. In the future, there is a trend of fusion between smart cabin SoC and smart driving SoC chips under the centralized E/E architecture.

“Reliable and Trustworthy”

With the continuous increase of functional safety and network security requirements, the reliability and trustworthiness of SoC chips is the primary concern. The implementation of reliability technology is based on fault tolerance, which mainly relies on the organization of redundant resources and system restructuring. Redundancy mainly includes hardware redundancy, software redundancy, time redundancy, information redundancy, and so on. Hardware redundancy adds some standby additional hardware outside the conventional hardware function design. When the conventional hardware fails, the standby hardware takes effect, allowing the system to continue working normally. Software redundancy adds some additional programs for checking and correcting errors. When an error occurs during operation, the program can automatically check and correct it. Time redundancy separates some extra time for a particular instruction or program to repeat its execution. Information redundancy increases the redundancy of information, giving it the ability to check and correct errors by itself.## How can domestic SoCs break through?

In the short term, relying on their first-mover advantage, scale of social networks, and speed of iteration, Qualcomm and NVIDIA are currently unchallenged in the intelligent cockpit and intelligent driving fields respectively. How can domestic SoC companies break through the competitive landscape and stand shoulder to shoulder with them?

First of all, it is necessary to focus on the user’s needs and build an innovative management process. Take autonomous driving AI chips as an example: many chip companies in the current market are based on their own algorithm development IP, and users who buy their chips must also use their algorithm. Some chip companies’ products cannot even support the CNN+Transformer algorithm, while others will continue to track forward visual learning algorithms during the design process to ensure compatibility. In addition, they also provide toolchain support to help customers build their own algorithm IP, in order to create a smart driving SoC with higher operational efficiency that is exclusive to the customer.

Secondly, it is necessary to build a high-level technical team. The chip industry itself is a systematic and engineering field, with a requirement for professional disciplines that are highly and widely inclusive, including but not limited to mathematics, chemistry, physics, imaging, and optics. The complexity and breadth represent greater challenges to engineers’ solid theoretical foundations and outstanding engineering capabilities! Therefore, reasonable division of work content and high-quality talent are the important soul of chip design companies, as well as the cornerstone of developing the positive ability of chip design.

Thirdly, for intelligent cockpit chips, as a series of intelligent cockpit scenarios, such as the car interior metaverse, non-touch interaction, and cabin docking, are landing, the development of intelligent cockpit SoC’s computing power trend is generally keeping up with PC. The main cockpit chips currently on the market will be replaced by higher computing power SoCs in the process of replacement. Smart driving SoC chips that pursue ultimate computing power will be favored by the market.

Fourth, for intelligent driving AI chips, while computing power is constantly improving, it also brings about significant increases in power consumption, cost, and area. Therefore, relying solely on chip computing power stacking cannot solve the support problem of intelligent driving system computing platforms. In the author’s opinion, unlimited expansion of computing power will not be a future trend. Compared with computing power of thousands of TOPS, precise and efficient AI computing power, as well as better software training, will become more important to save development cycles and costs for automakers.Dickens once said in “A Tale of Two Cities”: “It was the best of times, it was the worst of times.” During the process of the new electronic and electrical architecture revolution, there will be a profound change in the market pattern of the vehicle SoC. It is too early to draw conclusions about who will dominate in the future. However, Cao sir believes that chip companies that focus on user needs and deeply cultivate technology will definitely have more opportunities!

This article is a translation by ChatGPT of a Chinese report from 42HOW. If you have any questions about it, please email bd@42how.com.