Since 2022, a new concept has emerged in the smart car industry – integrated driving and parking, which refers to the use of a set of hardware to simultaneously achieve driving and parking functions.

This concept arose as a result of the evolution of automotive electronic electrical architecture from distributed to domain centralized, involving algorithm companies, chip manufacturers, domain controller solution providers, and host factories.

To study this hottest topic, “Automotive Industry Heart” launched the “Integrated Driving and Parking” special issue, hoping to clarify the latest technology roadmap and related solutions for integrated driving and parking from a diverse perspective.

At the 2019 Shanghai Auto Show, a pure electric sports car drew the attention of attendees.

With its sleek styling, slender physique, and frameless doors… various novel designs instantly caught everyone’s attention.

Yes, this was the scene of the debut of the new XPeng P7.

However, the highlight of this car does not stop there. Its level of intelligence is even more noteworthy.

Especially the Nvidia Xavier chip, which is claimed to be the first to be mounted in a domestic car on XPeng P7, has aroused people’s interest.

Some netizens even came to the auto show specifically to learn about the chip used in XPeng P7. Afterwards, he shared this information online.

With the addition of the Xavier chip, XPeng P7 has achieved functions such as entering and exiting ramps at high speeds, automatic parking at low speeds, and valet parking. Thus, it has taken the lead among new automakers to win the label of “intelligence” with the “driving + parking” function integrated on one chip. This is precisely what “integrated driving and parking” is all about, and XPeng P7 fired the first shot.

Afterward, the Ideal One 2021 version, SAIC’s third-generation Roewe RX5, the 2023 Kiwi EV version from DJI, and others have also launched “integrated driving and parking” functions based on different solutions, and more models have joined in the development to this day.

From the supplier’s perspective, at least 20 autonomous driving companies have released intelligent driving solutions that support integrated driving and parking, most of which will be put into mass production in the next two years.In the article “The Integration of Driving and Parking Finally Explained” on the Automotive Heart website, the specific implementation path of the software aspect of the integration of driving and parking is discussed from the perspective of algorithm development companies such as Nullmax and Niuha.

In fact, the relationship between the integration of driving and parking and chips is more direct.

As the carrier of algorithms, chips play a more fundamental role. To some extent, the selection of chips determines most of the performance of the integration of driving and parking.

Chip Manufacturers, the Secret Players behind the Integration of Driving and Parking

According to the industry’s general consensus, the integration of driving and parking involves the reuse of sensors and sharing of computing resources, both of which are related to the architecture of chips.

In the past, in the case of separation of driving and parking, the driving function could only call the driving chips and sensors, such as front cameras and millimeter-wave radars, while the parking function could only call the parking chips and sensors, such as fisheye cameras and ultrasonic radars.

Now, to achieve the integration of driving and parking, the fisheye camera must be called during driving, which can increase the passage rate of vehicles in congested follow-distance situations and cut-in scenarios, while the front camera must be called during parking, which can improve the forward perception ability of vehicles and identify obstacles on the road.

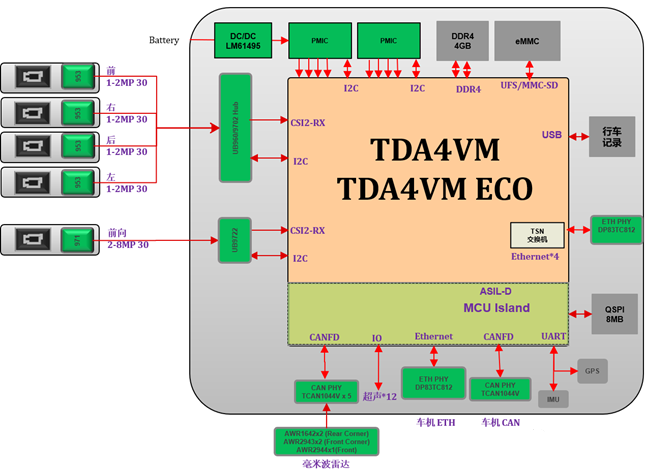

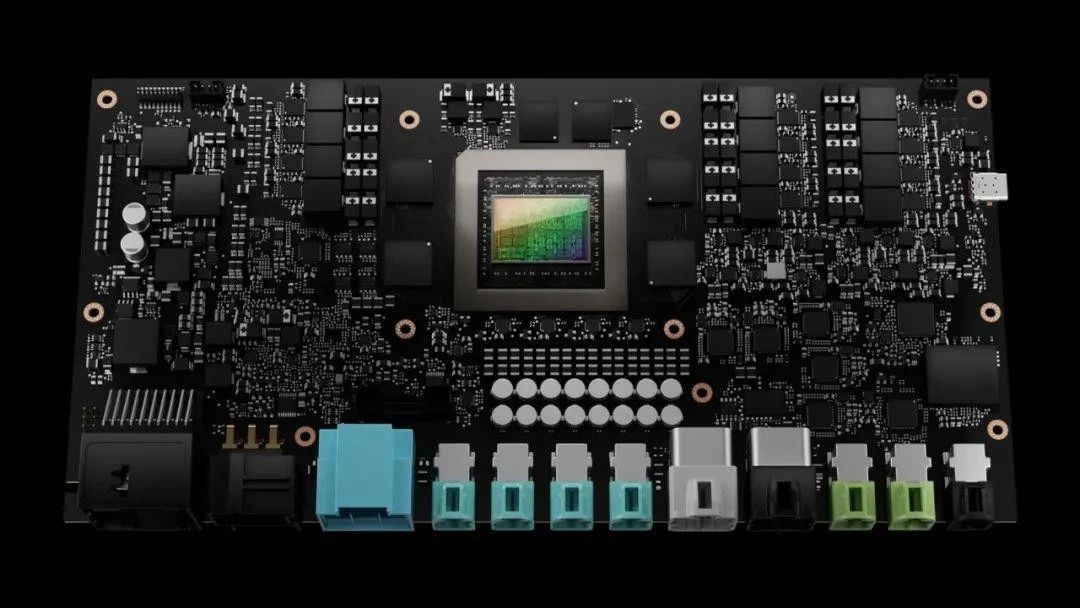

This means that enough sensor interfaces, including multiple camera inputs and multiple Ethernet device inputs (the main interfaces of laser radar and 4D millimeter-wave radar), and multiple CAN interface device inputs (the interface of 3D millimeter-wave radar), must be reserved on a single SoC.

The internal heterogeneous types of chips must also be designed accordingly.

For example, in the driving scene, the data fusion of cameras and millimeter-wave radar and map positioning require CPU and DSP with sufficient computing power to complete, while rendering and image stitching of 3D panoramic views must be done using GPUs in the parking scene.

In other words, SoC chips designed for driving and parking integration functions basically need to simultaneously integrate processor units such as ISP, GPU, MCU, CPU, and DSP.The Director of Intelligent Products at Heizhima, Wang Zhizhong, further explained:

“CPU resources are used for multitasking scheduling and sensor fusion, while ISP adjusts the RAW image signal output from multiple cameras. The DSP, together with the AI accelerator, can release a large portion of ARM resources.”

Among these components, the AI accelerator represented by the GPU is the core of the chip, responsible for large-scale parallel floating-point calculations.

The commonly mentioned computing power of a certain chip in the industry, measured in TOPS, refers to the theoretical value calculated by using the speed of multiplication and addition between the convolution and input matrices performed by the AI core of the chip as a reference during convolution neural network calculations.

Based on the size of the chip’s computing power, two types of integrated solutions have been developed: the “Lightweight Row Boat Integrated Solution” (computing power of around 20 TOPS) and the “Advanced Row Boat Integrated Solution” (over 100 TOPS with no upper limit).

The difference between the two lies in the type and number of sensors they support, as well as in the complexity of the neural network models they can run, which lead to different usage scenarios and experiences.

For example, Nullmax’s row boat integrated solution, based on the TI single TDA4VM chip, uses two forward-facing cameras, four fish-eye cameras, five millimetre-wave radars, and 12 ultrasonic radars as its sensor configuration. With 8 TOPS of AI computing power, it can provide a series of driving and parking functions, such as navigation assistance, high-speed driving assistance, traffic jam following, and automated parking.

By using the standard version of NVIDIA Orin (110 TOPS) chip, Nullmax can provide a more advanced driving experience, similar to that of Tesla’s FSD, which can be run on urban roads without relying on high-precision maps. In addition to all the above functions, it is equipped with more sensors.

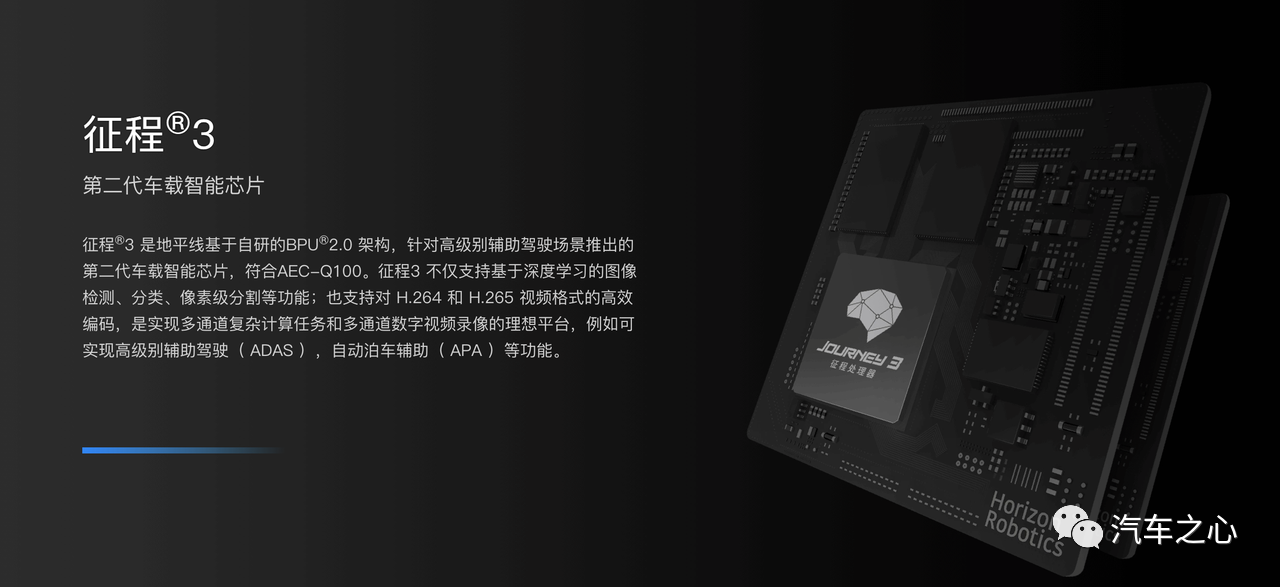

Due to its focus on a larger number of mid-to-low-end car models, the lightweight row boat integrated solution has a broader market. This is a fiercely competitive area for chip manufacturers such as TI, Heizhima, Horizon Robotics, and Cambricon, whose leading products are TDA4 (8 TOPS), A1000L (16 TOPS), J3 (5 TOPS), and SD5223 (with a maximum computing power exceeding 16 TOPS).

“`

“`

Among them, TDA4 can be considered a “hot item”.

According to data statistics, currently, among the models equipped with parking and driving integrated solution in the price range of 100,000 to 200,000 yuan in China, the percentage of models equipped with TDA4 is 40%-50%.

Numerous autonomous driving solution companies such as Nullmax, Baidu, DJI, and MAXIEYE are also developing parking and driving integrated solutions based on the TDA4 chip.

Black sesame A1000L and Horizon J3 are also very trending, and autonomous driving solutions based on a single A1000L, “J3+TDA4VM”, double “J3”, and triple “J3” are in the process of being installed.

The Harbin Institute of Technology is due to release the SD5223 this year, which is aimed at the L2+ level autonomous driving market and supports autonomous driving systems to cover entry-level car models priced at around 100,000 yuan.

High-end parking and driving integrated solutions are also experiencing a huge boom.

NVIDIA Orin-X, Black sesame A1000/A1000Pro/ A2000, and Horizon J5 are all targeting this market. For example, 2 NVIDIA Orin-X chips support Ideal L9, with a total of 508 TOPS in computing power, supporting automatic parking, intelligent city driving, remote calling, OTA upgrades, and other scenarios and functions.

At the end of September 2022, Ideal L8 was released, and Horizon J5 debuted globally on this model.

Looking forward to 2022: Horizon Robotics and BYD cooperate to bring J5 to some models, and Black Sesame’s A1000 series chip wins mass production for some car companies’ driving and parking integration programs.

By analyzing the product layout of various manufacturers, we can get a glimpse of what kind of chip is needed for driving and parking integration.

First of all, for lightweight driving and parking integration, the chip needs to balance the relationship between performance, power consumption, and cost.

In terms of performance, the main factor is the heterogeneous multi-core design of the SoC. As for how strong each core is, it varies from chip manufacturer to chip manufacturer.

“For example, some SoC chips only have 1 or 2 DSPs inside, and DSPs may all be allocated to traditional CV image processing. However, Black Sesame chips have 4 large DSPs inside, which not only do a lot of image and laser algorithm processing, but also take on the real-time management of the neural network accelerator, greatly releasing CPU resources.” Dayue Tian, Black Sesame’s senior product manager of intelligent automation, said.

Similarly, TDA4 has also been favored by many schemers because of its excellent design.

It adopts a multi-core heterogeneous structure, equipped with different types of processors including Cortex A72, Cortex R5F, DSP, MMA, and so on, and processes different tasks by the corresponding core or accelerator, such as logical computing power and AI computing power, which is more efficient.

In the chip design stage, Horizon Robotics also laid out the underlying unit logic required for the architecture as a whole. Firstly, it decomposed complex calculations into several small and parallelizable calculations. At the same time, it can also break down the instruction set that used to be processed serially into several parallel pipeline modes through the analysis of the compiler, thus reducing the computation delay and improving efficiency.

Under the Bayesian computational architecture called “Bayes” by Horizon Robotics, the J5 chip can still maintain stable and efficient data processing under the large throughput capability of multiple data streams.

Power consumption is also an important indicator that affects chip performance and directly relates to cost.

Some say that power consumption is the biggest challenge for chip design companies. The reason behind this is that if the power is too high, it will cause the temperature of the chip to rise, which in turn will reduce its reliability.

“`Using a certain chip as an example, the maximum power consumption reaches 20W, which brings great trouble to solution vendors, leading to either not choosing the chip, or finding a way to solve the heat dissipation problem.

“For example, introducing liquid cooling, but this will cause higher system complexity and lead to cost increase,” said an industry insider.

In response to this, Cambricon Technologies proposed to use AI architectures with high energy efficiency ratios, which can achieve higher performance and lower power consumption than traditional GPGPU architectures, and adopt natural heat dissipation, effectively solving the problem of cost increase.

However, the overall cost of the chip still needs to be further compressed by relevant manufacturers. After all, the mainframe manufacturers who put lightweight Liangyue Poboy integrated on board are a group of people who are relatively sensitive to costs. Their requirements for the chip are not only good performance and low power consumption, but also price advantages.

For the high-end Liangyue Poboy integrated, the most basic requirement is of course that the computing power should be high enough. Sun Luyi, the senior director of software development of Ambarella, said that the CPU computing power should reach at least 150KDMIPS, and the AI computing power should be at least 100TOPS.

This is because the high-end Liangyue Poboy integrated scheme needs to access more roads and higher resolution cameras, and also needs to add 4D millimeter wave radar, lidar and other sensors, and the running neural network model needs to be larger and more complex, so the CPU computing power and AI computing power demand will increase by 7~10 times.

In addition, as smart cars are still evolving, high computing power chips need to be pre-embedded to adapt to OTA function updates in the later stage.

However, computing power is not the higher the better.

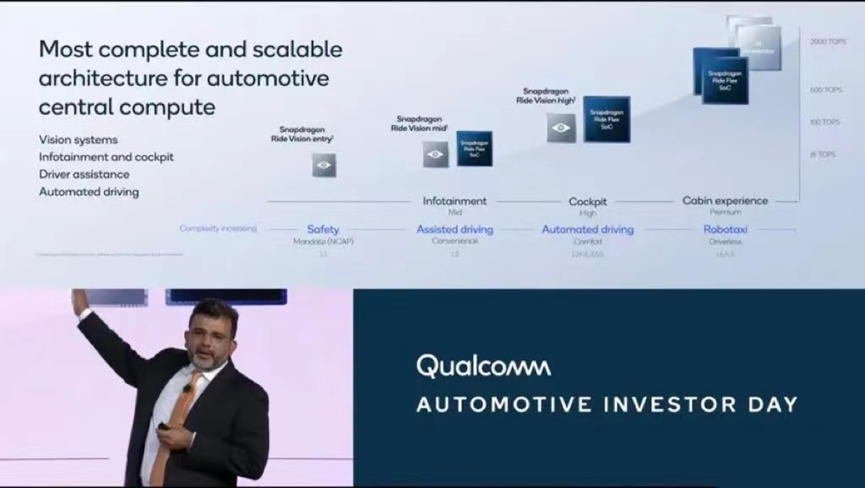

Recently, chip manufacturers seem to have opened a computing power war. For example, after Nvidia launched Thor, an autonomous driving chip with 2000TOPS computing power, Qualcomm immediately followed up and launched Ride Flex Premium SoC, with an external AI accelerator, and its comprehensive AI computing power can also reach 2000TOPS.

“`

“`

Actually, for autonomous parking, such high computing power is not required, and the more important indicator is chip utilization rate.

Industry insiders often criticize that the utilization rate of NVIDIA’s Xavier and Orin stays at around 30%, leading to significant waste of computing power.

On the other hand, Qualcomm’s autonomous driving chips, Mobileye, Huawei, and domestic control chip startups are taking the ASIC route, with higher utilization rates than NVIDIA’s GPU solution.

Power consumption is still a key concern for advanced autonomous parking systems, and chip manufacturers are still finding ways to reduce this value. The most direct method is to improve the chip-making process, moving from 6nm and 12nm to 7nm.

In January 2022, Qualcomm revealed that its Snapdragon Ride SoC will be built with 5nm process, becoming the industry’s first 5nm process autonomous driving chip.

By comparison, cost is no longer such a significant factor.

Models that use high-performance chips are generally positioned at the high end, such as the Ideal ONE (with two Orin-X chips), the XPeng P7 (with two Orin-X chips), the NIO ET7 (with four Orin-X chips), and the WEY Mocha (with a single Snapdragon Ride chip that has 360TOPS computing power), etc. The sensitivity to chip prices is much lower for car companies that use lightweight autonomous parking systems.

Chip manufacturers initiate the competition, and getting on board before 2025 is key

The realization of autonomous parking functions involves participants from the entire industrial chain of chip manufacturers, algorithm enterprises, domain controllers, and OEMs.

This means that the leading chip manufacturers not only need to refine their hardware products but also pay attention to the smooth “handover” in the rear.

Some domain controller manufacturers have criticized that the current chips are relatively complex, and there is no universal standard for SOC-end basic software platform products in the industry, which leads to low reusability of their solutions in different platforms.

To this end, Hei Zhima’s A1000L and A1000 use pin-to-pin platform design, and under the same software and hardware architecture, the computing power can be flexibly configured, reducing the expansion and upgrade costs of domain control platforms.

In addition, if chip manufacturers can provide supporting toolchains, software stacks, and so on, this will further facilitate the downstream development of autonomous parking functions.

“`One of the reasons for the popularity of TI’s TDA4 is that its toolchain is relatively mature, making it easier for related vendors to do secondary development based on it.

NVIDIA also released the NVIDIA DRIVE open source software stack, which has a complete toolchain and rich operator libraries; Horizon’s AI open platform – T-Head includes AI chip toolchains and AI application development middleware, as well as a model library; Black Sesame has released the Haian ADSP autonomous driving middleware platform;

Qualcomm stated that the Snapdragon Ride platform not only includes hardware, but also provides “secure middleware, operating systems, and drivers” for chips; Horizon Robotics will launch multiple autonomous driving SoC chips in the next two years and provide mature software toolchains.

Chip companies have become more active in the autonomous driving industry chain, and now they will directly face automakers to help Tier1 win projects or directly cooperate with automakers.

Through this form, chip companies can not only directly demonstrate some capabilities of their chips to automakers, but also directly obtain some demands from automakers, such as the requirements for the expandability of domain controllers, chip interfaces, computing resources, and other demands, so that they can adjust their product strategy directions more timely.

Today, chip companies’ position in the autonomous driving industry chain is increasing, especially for large-scale computing vendors to directly cooperate with automakers.

Generally speaking, the two sides will jointly develop the functions of parking and berthing, for example, the chip manufacturer provides “hardware + development tools” support, and the automaker self-develops upper-layer algorithms based on it. However, some automakers require a one-stop solution that combines hardware and software for parking and berthing to be quickly mass-produced, which requires chip manufacturers to have a “full package” ability from hardware to algorithms.

A Qualcomm spokesperson made it clear:

“For some automakers, if their software development capabilities are weak and the development costs of third-party traditional Tier1 suppliers are too high, we can directly provide a complete ADAS turnkey solution.”Except for algorithm ability, other “soft power” of chip manufacturers are also very important.

For example, product consistency, reliability, and supply chain availability are precisely the strengths of old enterprises such as TI.

Among the traditional suppliers of car-grade chip supply, TI has absolute R&D experience, and its chip reliability has been verified for a long time, so car companies trust it more.

In terms of supply, previous host factories or domain control Tier1 have encountered shortages of MCU from major factories such as Infineon, resulting in huge losses. However, TI’s TDA4 VM chip contains an MCU core, which relieves their concerns about ensuring the supply of car-grade MCUs.

It can be seen that the combination of parking and driving brings about a comprehensive competition of chip manufacturers’ capabilities. With the successive announcement of car manufacturers, this competition has entered a more intense stage.

According to incomplete statistics, at least 20 autonomous driving companies have released intelligent driving solutions supporting the combination of parking and driving. Most of them will be mass-produced and landed in the next two years.

“The main SOC determines the hardware architecture, software architecture, and algorithm system of the new generation of intelligent driving platform for car companies. Once selected, car companies will not switch unless necessary.”

Insiders said that the cost of cultivating mature suppliers for host factories is extremely high, which has led to the current “internal competition” of chip manufacturers.

In Heizhima’s view, 2025 is a critical point for domestic autonomous driving chip players. After that, the domestic supply chain system will be completed, and “every pit will start to have carrots.”

Currently, Heizhima A1000, Horizon J5, and NVIDIA Orin are competing for mass production, and Horizon Song SD5226 will also be unveiled soon. With intensified competition, there is already little window of opportunity left for other chip manufacturers.

This article is a translation by ChatGPT of a Chinese report from 42HOW. If you have any questions about it, please email bd@42how.com.